Segmented Ladder Bus Control Design Achieves Scalable, Energy-Efficient Communication for Large-Scale Architectures – Quantum Zeitgeist

Report on a Novel Control System for Sustainable Large-Scale Computing

A new control system for segmented ladder bus interconnects has been developed, addressing critical challenges in large-scale computing. This research, conducted by Phu Khanh Huynh, Francky Catthoor, and Anup Das, introduces a design methodology that significantly enhances the efficiency of data flow management. The innovation directly supports several United Nations Sustainable Development Goals (SDGs) by optimizing energy consumption, reducing the physical footprint of hardware, and fostering sustainable technological infrastructure.

Technological Innovation and Sustainable Infrastructure (SDG 9)

The research presents a significant advancement in digital infrastructure, aligning with SDG 9 (Industry, Innovation, and Infrastructure), which calls for building resilient infrastructure and fostering innovation. The developed control plane for segmented ladder bus architectures provides a more efficient and scalable solution for communication between processing tiles, a foundational element of modern computing systems.

A Novel Control System for Neuromorphic Computing

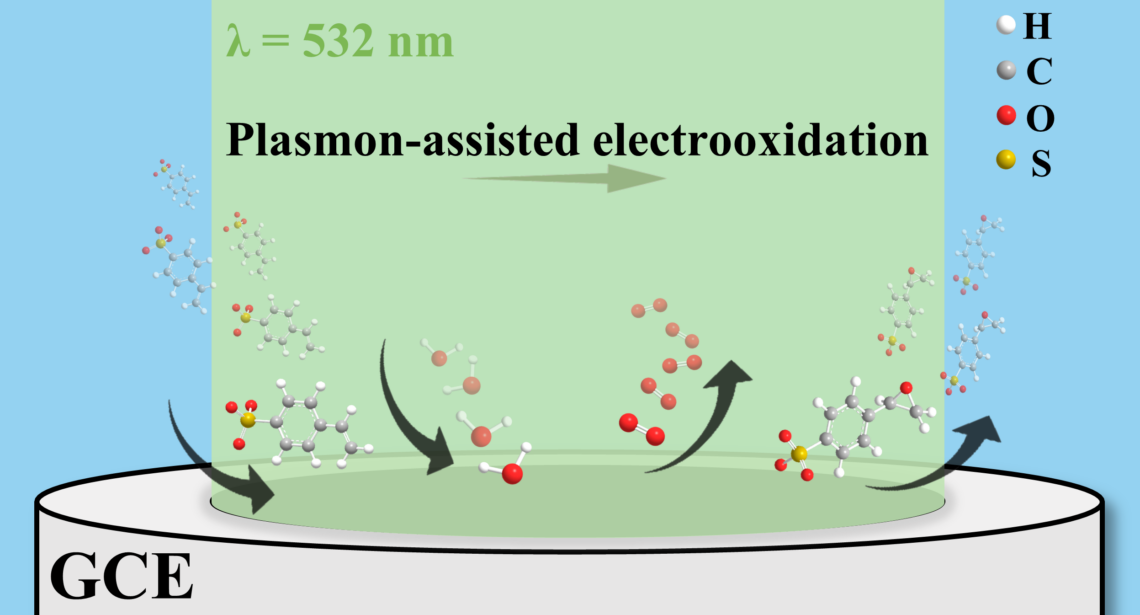

The control system is specifically tailored for the sparse and asynchronous communication patterns found in neuromorphic computing systems. These brain-inspired architectures require interconnects that can handle intense bursts of activity while minimizing power consumption during idle periods. The segmented ladder bus is an ideal candidate due to its simplicity and energy efficiency, but its potential was previously limited by the lack of a streamlined and scalable control mechanism.

Design Methodology and Optimization

The core of the innovation is a scenario-aware control plane that adapts to application-specific traffic patterns. This methodology contributes to sustainable industrialization and innovation by creating more efficient systems.

- Compile-Time Traffic Analysis: The system analyzes communication patterns before execution to identify frequently occurring scenarios.

- Scenario Reduction: By focusing on common patterns, the control plane minimizes the number of active control scenarios it must manage.

- Optimized Control Plane: This reduction in complexity leads to a smaller control plane in terms of both memory requirements and hardware overhead.

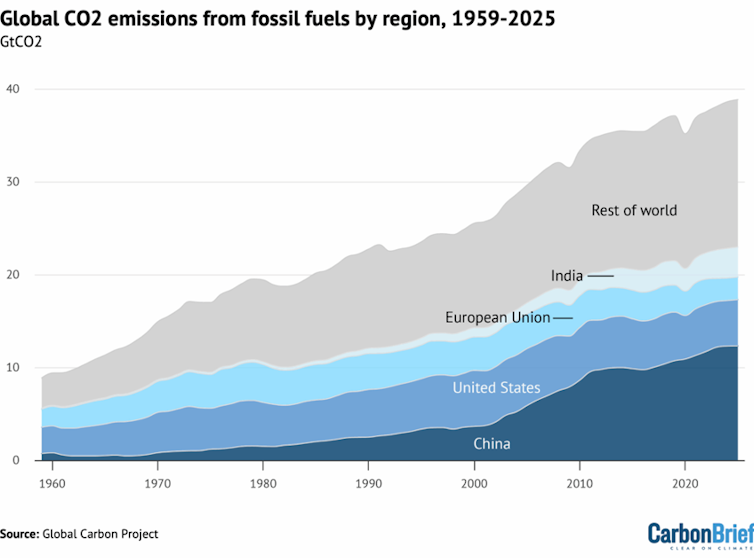

Advancing Energy Efficiency and Climate Action (SDG 7 & SDG 13)

A primary achievement of this research is the significant reduction in power consumption, a direct contribution to SDG 7 (Affordable and Clean Energy) and SDG 13 (Climate Action). By improving the energy efficiency of large-scale computing, this work helps reduce the overall carbon footprint of digital technologies.

Minimizing Power Consumption

The control system’s design inherently promotes energy efficiency. By streamlining the control process and adapting to traffic bursts, it ensures that the communication infrastructure consumes minimal power, particularly during periods of inactivity common in neuromorphic applications. This is a critical step toward doubling the global rate of improvement in energy efficiency as targeted by SDG 7.3.

Resource Efficiency and Scalability for Sustainable Systems (SDG 11 & SDG 12)

The research promotes responsible consumption and production patterns (SDG 12) by creating hardware that is more efficient in its use of physical resources. The resulting scalable and efficient computing architectures are essential for developing sustainable cities and communities (SDG 11).

Scenario-Aware Control and Reduced Footprint

The scenario-aware optimization yields a substantial reduction in the control plane’s physical area relative to the data plane. This contributes to SDG 12 by reducing the material required for manufacturing complex computing hardware.

- The control plane consumes less than 10% of the total network resources.

- The area footprint is significantly smaller than the data plane it manages.

- Reduced memory storage requirements lower the overall size and complexity of the system.

Validation and Scalability Analysis

The design was validated through a combination of hardware implementation on a field-programmable gate array (FPGA) and software-based simulations. The results confirmed the system’s effectiveness and scalability.

- Substantial Overhead Reduction: Experiments demonstrated a significant decrease in resource overhead without compromising reliable data transmission.

- Proven Scalability: Analysis revealed that the control complexity grows more slowly than network connectivity, indicating that the solution is highly scalable for future large-scale systems.

Conclusion

This research successfully demonstrates a scalable, resource-efficient, and energy-efficient control mechanism for dynamic segmented buses. The innovation paves the way for larger and more complex neuromorphic computing architectures while making a direct contribution to global sustainability targets. By advancing technological infrastructure (SDG 9) that is both energy-efficient (SDG 7) and resource-conscious (SDG 12), this work supports the development of sustainable systems essential for climate action (SDG 13) and future smart communities (SDG 11).

1. Which SDGs are addressed or connected to the issues highlighted in the article?

SDG 9: Industry, Innovation, and Infrastructure

The article is fundamentally about scientific research and technological innovation. It describes a “novel control system” and a “new control methodology” developed by researchers to improve large-scale computing architectures. This directly relates to fostering innovation and upgrading technological infrastructure, which are central to SDG 9.

SDG 7: Affordable and Clean Energy

A primary goal of the research is to improve energy efficiency. The article repeatedly mentions aims such as “minimising its size and power consumption,” developing an “energy-efficient” interconnect, and handling communication bursts “while minimizing power consumption during idle times.” This focus on reducing energy use in high-performance computing aligns with SDG 7.

SDG 12: Responsible Consumption and Production

The research emphasizes resource efficiency by reducing the physical size and material requirements of computing components. The article highlights a “substantial reduction in the control plane’s area” and minimizing “hardware overhead.” This contributes to more sustainable production patterns in the electronics industry by using fewer materials to achieve the same or better performance, which is a core principle of SDG 12.

2. What specific targets under those SDGs can be identified based on the article’s content?

Under SDG 9: Industry, Innovation, and Infrastructure

-

Target 9.4: By 2030, upgrade infrastructure and retrofit industries to make them sustainable, with increased resource-use efficiency and greater adoption of clean and environmentally sound technologies and industrial processes.

- The article describes an innovation that makes computing infrastructure more sustainable by increasing its energy and resource efficiency. The development of a control plane that is “lightweight, consuming less than 10% of total network resources” is a direct example of upgrading infrastructure with a focus on resource-use efficiency.

-

Target 9.5: Enhance scientific research, upgrade the technological capabilities of industrial sectors in all countries…encouraging innovation.

- The article is a report on scientific research conducted at Drexel University and the National Technical University of Athens. This research pioneers a “first-of-its-kind design” that upgrades the technological capabilities of neuromorphic computing systems, directly reflecting the goal of this target.

Under SDG 7: Affordable and Clean Energy

-

Target 7.3: By 2030, double the global rate of improvement in energy efficiency.

- The research contributes to this target by creating a system that is explicitly more energy-efficient. The segmented ladder bus is described as a “promising interconnect architecture known for its simplicity and energy efficiency,” and the new control plane optimizes it further to “minimize power consumption.”

Under SDG 12: Responsible Consumption and Production

-

Target 12.2: By 2030, achieve the sustainable management and efficient use of natural resources.

- The technology described leads to a more efficient use of physical resources. By achieving a “substantial reduction in the control plane’s area compared to the data plane” and reducing “control memory and hardware overhead,” the design requires fewer raw materials for manufacturing, contributing to the efficient use of natural resources.

3. Are there any indicators mentioned or implied in the article that can be used to measure progress towards the identified targets?

The article implies several quantifiable indicators that can be used to measure progress towards the identified targets.

Indicators for SDG 9 (Targets 9.4 and 9.5)

- Reduction in resource overhead: The article explicitly states the control plane consumes “less than 10% of total network resources.” This percentage serves as a direct, measurable indicator of increased resource efficiency in technological infrastructure.

- Scalability metric: The finding that “control complexity grows more slowly than network connectivity” is a measurable indicator of the technology’s scalability and its suitability for future, larger-scale infrastructure.

Indicators for SDG 7 (Target 7.3)

- Power consumption during idle times: The stated goal to “minimize power consumption during idle times” implies that a key performance indicator is the measurement of energy usage in watts during periods of inactivity in the computing system.

- Overall energy efficiency: The article refers to the architecture’s “energy efficiency.” This can be measured as computations per unit of energy (e.g., GFLOPS/watt) to track improvements.

Indicators for SDG 12 (Target 12.2)

- Ratio of control plane area to data plane area: The “substantial reduction in the control plane’s area compared to the data plane” is a quantifiable indicator. This ratio can be measured to demonstrate more efficient use of silicon or other substrate materials.

- Memory storage requirements: The design’s ability to “minimize memory storage requirements” can be measured in kilobytes or megabytes. The reduction in required memory is a direct indicator of dematerialization and resource efficiency.

4. Create a table with three columns titled ‘SDGs, Targets and Indicators” to present the findings from analyzing the article.

| SDGs | Targets | Indicators |

|---|---|---|

| SDG 9: Industry, Innovation, and Infrastructure |

9.4: Upgrade infrastructure for sustainability and resource-use efficiency.

9.5: Enhance scientific research and upgrade technological capabilities. |

|

| SDG 7: Affordable and Clean Energy | 7.3: Double the global rate of improvement in energy efficiency. |

|

| SDG 12: Responsible Consumption and Production | 12.2: Achieve the sustainable management and efficient use of natural resources. |

|

Source: quantumzeitgeist.com

What is Your Reaction?

Like

0

Like

0

Dislike

0

Dislike

0

Love

0

Love

0

Funny

0

Funny

0

Angry

0

Angry

0

Sad

0

Sad

0

Wow

0

Wow

0